# AKD4103A-B

# **AK4103A Evaluation Board Rev.0**

#### **GENERAL DESCRIPTION**

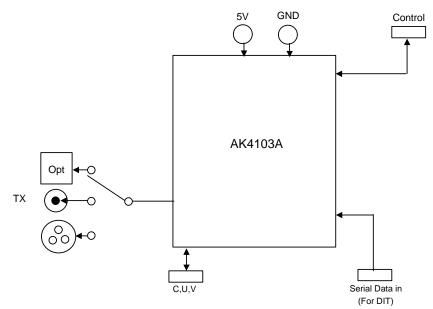

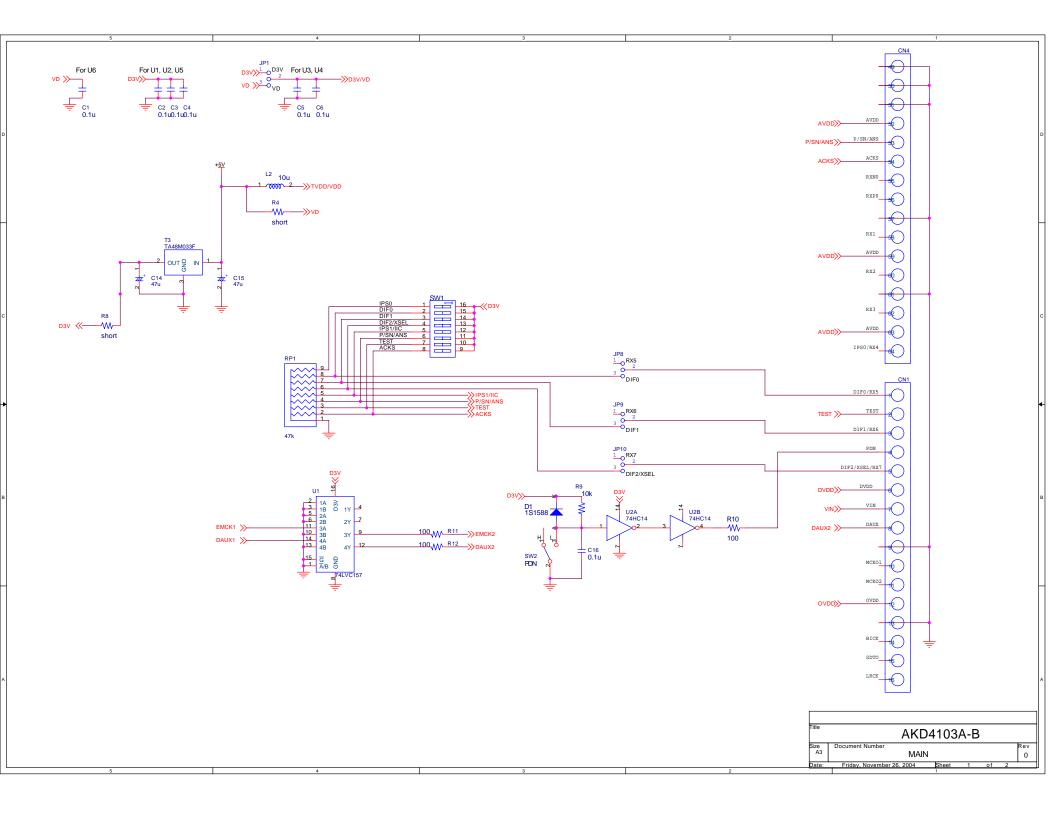

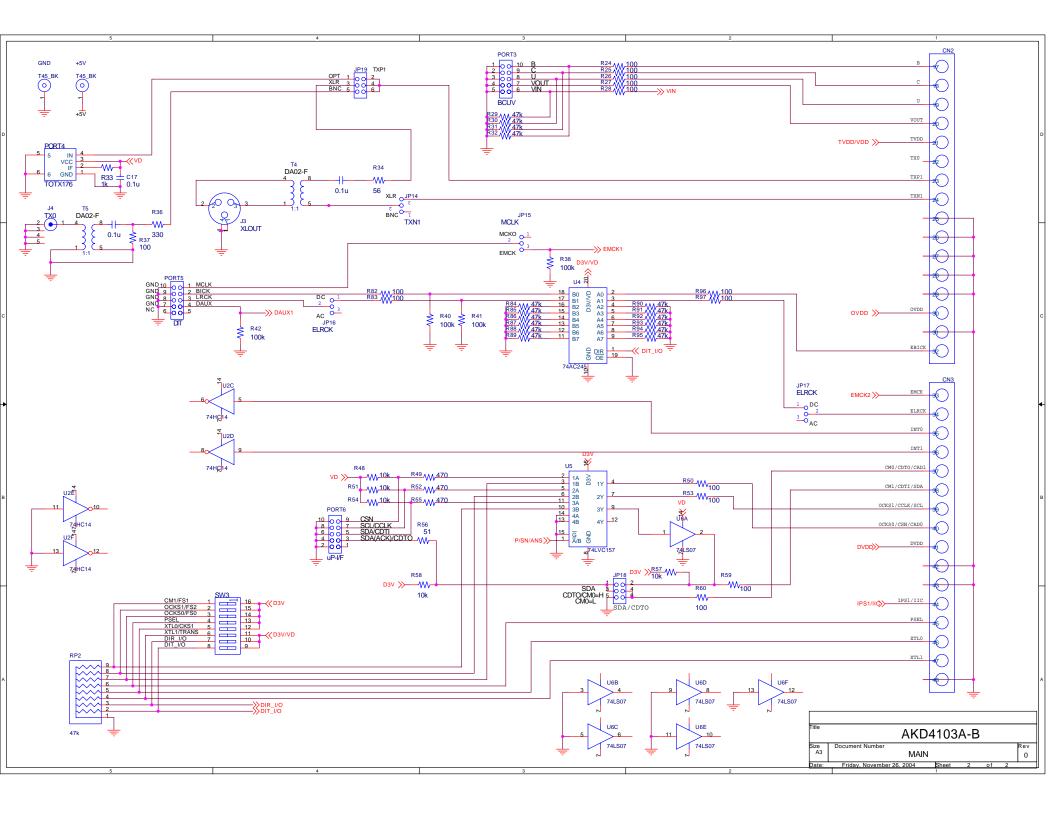

The AKD4103A-B is an evaluation board for the AK4103A, 192kHz DIT. The AKD4103A-B has the interface with AKM's A/D converter evaluation boards and AKM's DIR evaluation boards. Therefore, it is easy to evaluate the AK4103A. The AKD4103A-B also has the digital audio interface and can achieve the interface with digital audio systems via optical link, BNC unbalance or XLR balance connector.

#### ■ Ordering guide

AKD4103A-B --- Evaluation board for AK4103A

(A cable for connecting with printer port of IBM-AT compatible PC and a control software are packed with this. The control software does not operate on Windows NT.)

#### **FUNCTION**

- □ Digital interface

- ☐ Compatible with 2 types of interface

- Direct interface with AKM's ADC, DIR evaluation boards by 10pin header

- Optical/BNC/XLR output

- ☐ Serial control data I/F

- 1 input/output port (10-pin port)

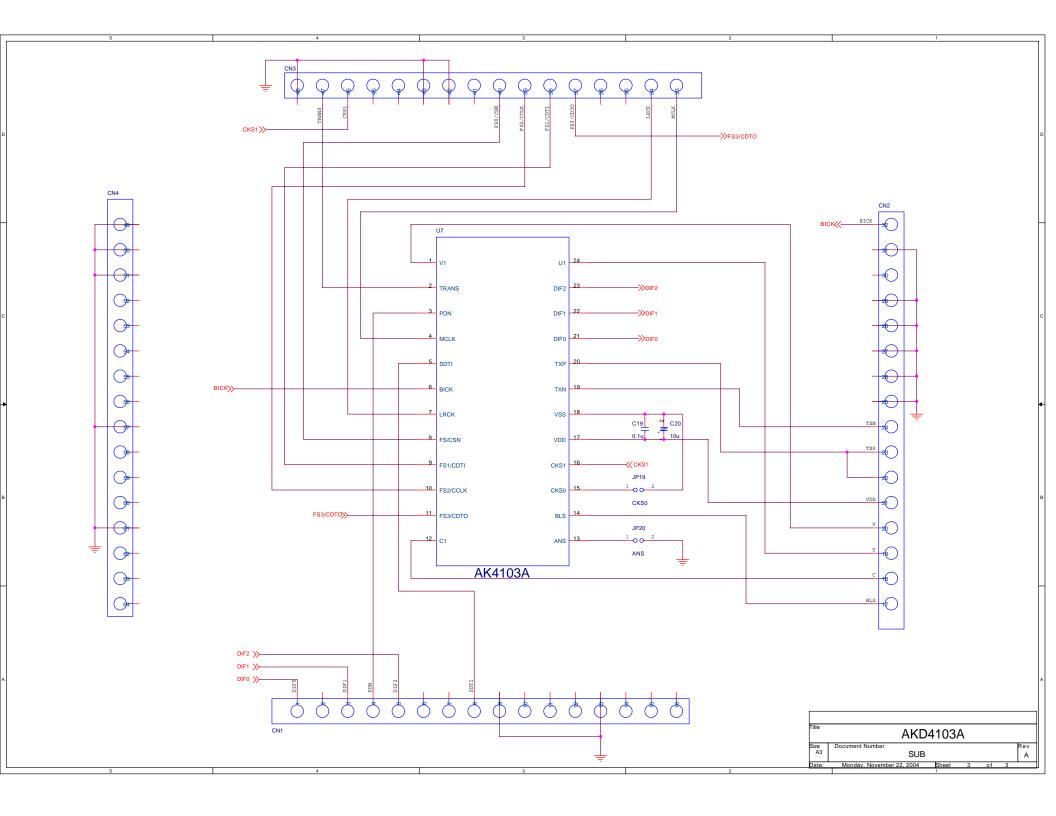

Figure 1. AKD4103A-B Block Diagram \*Circuit diagram and PCB layout are attached at the end of this manual.

- 1 -

#### **Evaluation Board Manual**

#### **■** Operating sequence

(1) Set up the power supply lines.

[+5V] (Red) = 5V [GND] (Black) = 0V

(2) Set up the evaluation mode and jumper pins. (Refer to the following item.)

(3) **Connect cables.** (Refer to the following item.)

(4) Power on.

The AK4103A should be reset once bringing PDN(SW2) "L" upon power-up.

#### **■** Evaluation modes

(1) Evaluation for DIT

Serial Data in(10pin port) – AK4103A – S/PDIF out(optical or BNC)

MCLK, BICK, LRCK and SDTI are input the via 10pin header (PORT5: DIT). The AKD4103A-B can be connected with the AKM's DAC evaluation board via 10-line cable.

a. Set-up of a Bi-phase output signal

| Connector       | JP19 (TXP) |

|-----------------|------------|

| Optical (PORT4) | OPT        |

| XLR (J3)        | XLR        |

| BNC (J4)        | BNC        |

Table 1. Set-up of TXP

b. Set-up of clock input and output

The used signals are MCLK, LRCK, BICK and SDTI (DAUX).

The signal level outputted and inputted from PORT5 is 5V.

| Clock          | PORT  |

|----------------|-------|

| MCLK           | PORT5 |

| BICK           | PORT5 |

| LRCK           | PORT5 |

| SDTI<br>(DAUX) | PORT5 |

Table 2. Clock input/output

| CKS1 pin<br>(SW3_5) | CKS0 pin<br>(Sub_JP19) | MCLK  | fs (max)    |         |

|---------------------|------------------------|-------|-------------|---------|

| CKS1 bit            | CKS0 bit               |       |             |         |

| 0                   | 0                      | 128fs | 28k-192 kHz | Default |

| 0                   | 1                      | 256fs | 28k-108 kHz |         |

| 1                   | 0                      | 384fs | 28k-54 kHz  |         |

| 1                   | 1                      | 512fs | 28k-54 kHz  |         |

Table 3. Master Clock Frequency Select

# b-1. Set-up of input/output of BICK and LRCK

Please set up SW  $3_8$  (DIT\_I/O) according to the setup of audio format of AK4103A (Refer to Table 5).

| Audio format | SW3_8 (DIT_I/O) |

|--------------|-----------------|

| Slave mode   | 0               |

| Master mode  | 1               |

Default

Table 4. Set-up of DIT\_I/O

# c. Set-up of audio data format

It sets up by SW 1\_2, SW 1\_3 and SW1\_4 in synchronous mode. Please set up DIF2-0 bit in asynchronous mode.

| Mode | DIF2 pin<br>(SW1_4) | DIF1 pin<br>(SW1_3) | DIF0 pin<br>(SW1_2) | SDTI                    | LRCK |     | BICK     |     |

|------|---------------------|---------------------|---------------------|-------------------------|------|-----|----------|-----|

|      | DIF2 bit            | DIF1 bit            | DIF0 bit            |                         |      | I/O |          | I/O |

| 0    | 0                   | 0                   | 0                   | 24bit, Left justified   | H/L  | О   | 64fs     | О   |

| 1    | 0                   | 0                   | 1                   | 24bit, Left justified   | H/L  | О   | 64fs     | О   |

| 2    | 0                   | 1                   | 0                   | 24bit, Left justified   | H/L  | О   | 64fs     | O   |

| 3    | 0                   | 1                   | 1                   | 24bit, Left justified   | H/L  | О   | 64fs     | О   |

| 4    | 1                   | 0                   | 0                   | 24bit, Left justified   | H/L  | О   | 64fs     | О   |

| 5    | 1                   | 0                   | 1                   | 24bit, I <sup>2</sup> S | L/H  | О   | 64fs     | O   |

| 6    | 1                   | 1                   | 0                   | 24bit, Left justified   | H/L  | I   | 64-128fs | I   |

| 7    | 7 1 1 1             |                     | 1                   | 24bit, I <sup>2</sup> S | L/H  | I   | 64-128fs | I   |

Default

Table 5. Audio format

#### ■ B, C, U, V Inputs (at synchronous mode)

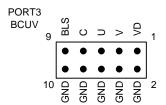

At synchronous mode (ANS=1), C(channel status), U(user data) and V(validity) are input via 10pin header (PORT3: BCUV). BLS is output at normal mode (TRANS=0), and is input at audio routing mode (TRANS=1). In case of audio routing mode, BLS, C, U an V can be directly input from the AKD4114 via 10-line flat cable. The pin layout of PORT3 is shown in Figure 2.

Figure 2. PORT3 pin layout

#### ■ Serial control

The AK4103A can be controlled by pins at synchronous mode (ANS=1) and by internal register at asynchronous mode (ANS=0). Synchronous/Asynchronous mode is set as Table 6.

| Mode         | SW1-6 (ANS) | JP18 (SDA/CDTO)                                               | Sub_JP20 (ANS) |

|--------------|-------------|---------------------------------------------------------------|----------------|

| Synchronous  | ON          | FS3=1: Short "CDTO/CM0=H" side.<br>FS3=0: Short "CM0=L" side. | Open.          |

| Asynchronous | OFF         | Short "CDTO/CM0=H" side.                                      | Short.         |

Default

Table 6. Synchronous/Asynchronous mode

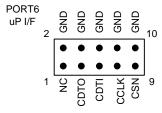

At asynchronous mode (ANS=0), the AK4103A can be controlled via the printer port (parallel port) of IBM-AT compatible PC. Connect PORT6 (uP-I/F) with PC by 10-line flat cable packed with the AKD4103A-B. Take care of the direction of connector. There is a mark at pin#1. The pin layout of PORT6 is shown in Figure 3.

Figure 3. PORT6 pin layout

Control software is packed with the AKD4103A-B. The software manual is included in this eva-board manual.

■ Toggle switch set-up

| CMO   | SW2 PDN | Reset switch for AK4103A. Set to "H" during normal operation. Bring to "L" once after |

|-------|---------|---------------------------------------------------------------------------------------|

| 3 W Z | PDN     | the power is supplied.                                                                |

■ DIP switch (SW1) set-up: -off- means "L"

| No. | Switch Name | Function                                                         | Default |

|-----|-------------|------------------------------------------------------------------|---------|

| 1   | IPS0        | Don't care                                                       | OFF     |

| 2   | DIF0        | Set-up of DIF0 pin. (in synchronous mode)                        | OFF     |

| 3   | DIF1        | Set-up of DIF1 pin. (in synchronous mode)                        | OFF     |

| 4   | DIF2        | Set-up of DIF2 pin. (in synchronous mode)                        | ON      |

| 5   | IPS1/IIC    | Don't care                                                       | OFF     |

| 6   | ANS         | Set-up of ANS pin. "L": asynchronous mode, "H": synchronous mode | OFF     |

| 7   | TEST        | Don't care                                                       | OFF     |

| 8   | ACKS        | Don't care                                                       | OFF     |

■ DIP switch (SW3) set-up: -off- means "L"

| No. | Switch Name | Function                                                                                                        | Default |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------|---------|

| 1   | FS1         | Compling frequency select at symphronous mode (ANS-1)                                                           | OFF     |

| 2   | FS2         | Sampling frequency select at synchronous mode (ANS=1).  (See the datasheet.)                                    | OFF     |

| 3   | FS0         | (See the datasheet.)                                                                                            | OFF     |

| 4   | PSEL        | Don't care                                                                                                      | OFF     |

| 5   | CKS1        | Set-up of CKS1 pin. (in synchronous mode)                                                                       | OFF     |

| 6   | TRANS       | Set-up of TRANS pin. "L": normal mode, "H": audio routing mode                                                  | OFF     |

| 7   | DIR_I/O     | Don't care                                                                                                      | OFF     |

| 8   | DIT_I/O     | Set-up of the transmission direction of 74AC245 "L": When inputting from PORT5, "H": When outputting from PORT5 | OFF     |

■ Jumper set up.

| No.     | Jumper Name | Function                                            |

|---------|-------------|-----------------------------------------------------|

|         |             | Set-up of Power supply source for 74AC245.          |

| 1       | D3V/VD      | D3V : D3V                                           |

|         |             | VD : VD (default)                                   |

|         |             | Set-up of FS3 pin                                   |

| 18      | SDA/CDTO    | Synchronous mode : short "CDTO/CM0=H" → FS3 pin="H" |

| 18      | SDA/CDTO    | short "CM0=L" → FS3 pin="L"                         |

|         |             | Asynchronous mode: short "CDTO/CM0=H" (default)     |

|         | TXP1        | Set-up of TXP1 output circuit.                      |

| 10      |             | OPT : Optical (default)                             |

| 19      |             | XLR: XLR                                            |

|         |             | BNC : BNC                                           |

|         |             | Set-up of CKS0 pin                                  |

| 19(sub) | CKS0        | Open: CKS0 pin="H"                                  |

|         |             | Short : CKS0 pin="L" (default)                      |

|         |             | Set-up depending synchronous / asynchronous mode    |

| 20(sub) | ANS         | Open: synchronous mode                              |

|         |             | Short : asynchronous mode (default)                 |

#### **Control Software Manual**

#### ■ Set-up of evaluation board and control software

- 1. Set up the AKD4103A-B according to previous term.

- 2. Connect IBM-AT compatible PC with AKD4103A-B by 10-line type flat cable (packed with AKD4103A-B). Take care of the direction of 10pin header. (Please install the driver in the CD-ROM when this control software is used on Windows 2000/XP. Please refer "Installation Manual of Control Software Driver by AKM device control software". In case of Windows95/98/ME, this installation is not needed. This control software does not operate on Windows NT.)

- 3. Insert the CD-ROM labeled "AKD4103A-B Evaluation Kit" into the CD-ROM drive.

- 4. Access the CD-ROM drive and double-click the icon of "akd4103a-b0.exe" to set up the control program.

- 5. Then please evaluate according to the follows.

#### ■ Operation flow

Keep the following flow.

- 1. Set up the control program according to explanation above.

- 2. Click "Write default" button.

- 3. Then set up the dialog and input data.

#### ■ Explanation of each buttons

1. [Port Setup]: Set up the printer port.

2. [Write default]: Initialize the register of AK4103A.

3. [All Write]: Write all registers that is currently displayed.

4. [Read All]: All the registers of AK4103A are read.

5. [Function1]: Dialog to write data by keyboard operation.

6. [F3]: Dialog of sequential writing.

7. [SAVE]: Save the current register setting.

8. [OPEN]: Write the saved values to all register.

9. [Write]: Dialog to write data by mouse operation.

10. [Read]: The data corresponding to each register is read.

#### ■ Explanation of each dialog

1. [Function1 Dialog]: Dialog to write data by keyboard operation

Address Box: Input register address in 2 figures of hexadecimal.

Data Box: Input register data in 2 figures of hexadecimal.

If you want to write the input data to AK4103A, click "OK" button. If not, click "Cancel" button.

2. [Write Dialog]: Dialog to write data by mouse operation

There are dialogs corresponding to each register.

Click the "Write" button corresponding to each register to set up the dialog. If you check the check box, data becomes "H" or "1". If not, "L" or "0".

If you want to write the input data to AK4103A, click "OK" button. If not, click "Cancel" button.

#### ■ Indication of data

Input data is indicated on the register map. Red letter indicates "H" or "1" and blue one indicates "L" or "0". Blank is the part that is not defined in the datasheet.

# ■ Attention on the operation

If you set up Function1 dialog, input data to all boxes. Attention dialog is indicated if you input data or address that is not specified in the datasheet or you click "OK" button before you input data. In that case set up the dialog and input data once more again. These operations does not need if you click "Cancel" button or check the check box.

- 7 -

| Day Jalan I Parkana |

|---------------------|

| Revision History    |

| ite vision instally |

| Date<br>(YY/MM/DD) | Manual<br>Revision | Board<br>Revision | Reason        | Contents |

|--------------------|--------------------|-------------------|---------------|----------|

| 04/11/22           | KM076800           | 0                 | First edition |          |

#### IMPORTANT NOTICE

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or

other hazard related device or system, and AKM assumes no responsibility relating to any such use, except

with the express written consent of the Representative Director of AKM. As used here:

- (a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- (b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.

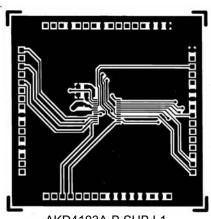

AKD4103A-B SUB L1

AKD4103A-B SUB L1\_SILK

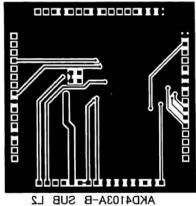

AKD4103A-B SUB L2\_SILK

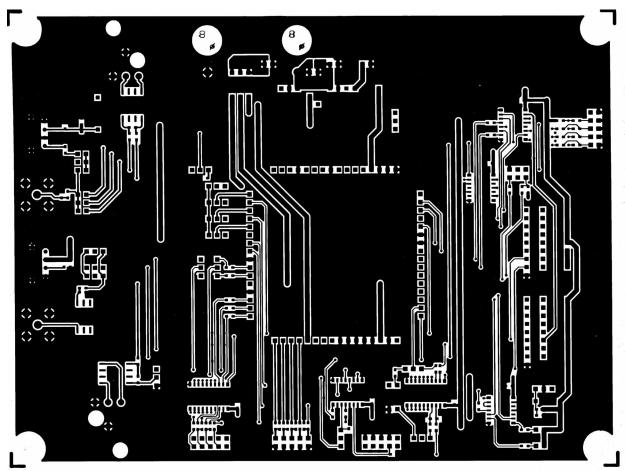

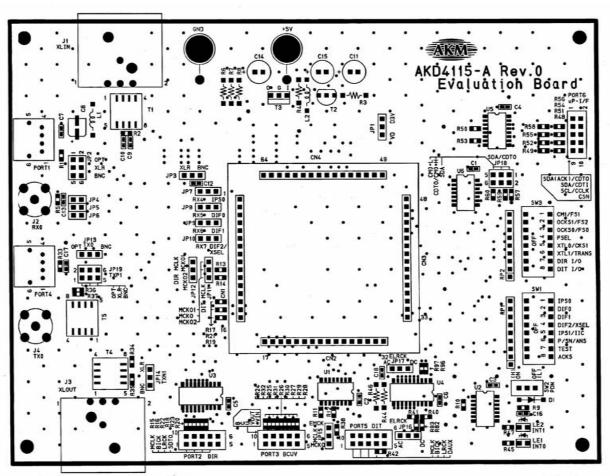

AKD4115-A L1

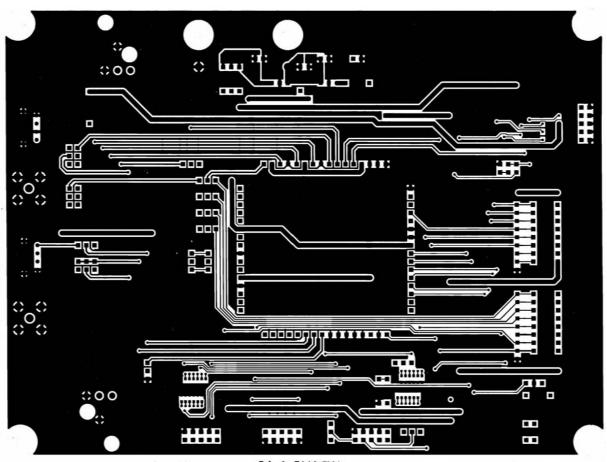

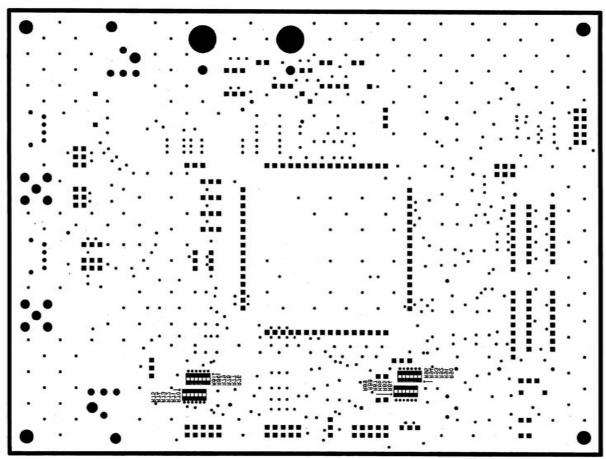

AKD4115-A L2

AKD4115-A L1\_SILK

AKD4115-A L2\_SILK